集體電路 (IC) 發明至今已有50多年,自1991年問世以來,國際半導體技術藍圖 (International Technology Roadmap for Semiconductors,ITRS) 一直是半導產業往前邁進的指南,藍圖預測半導體技術會遵循摩爾定律 (Moore’s Law) 的縮放節奏邁進。不過,在2016年7月ITRS所釋出的半導體產業「未來藍圖」報告顯示,估計微處理器中的電晶體體積將在 2021 年開始停止縮小,這意味著微處理器中的電晶體數量將不會再如摩爾定律所說的會逐步增加,也就是說摩爾定律已宣告死亡。隨著摩爾定律的死亡,國際半導體技術藍圖ITRS也將步入歷史。取而代之的,將是異質整合藍圖(Heterogeneous Integration Roadmap,HIR)。

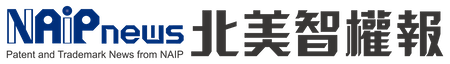

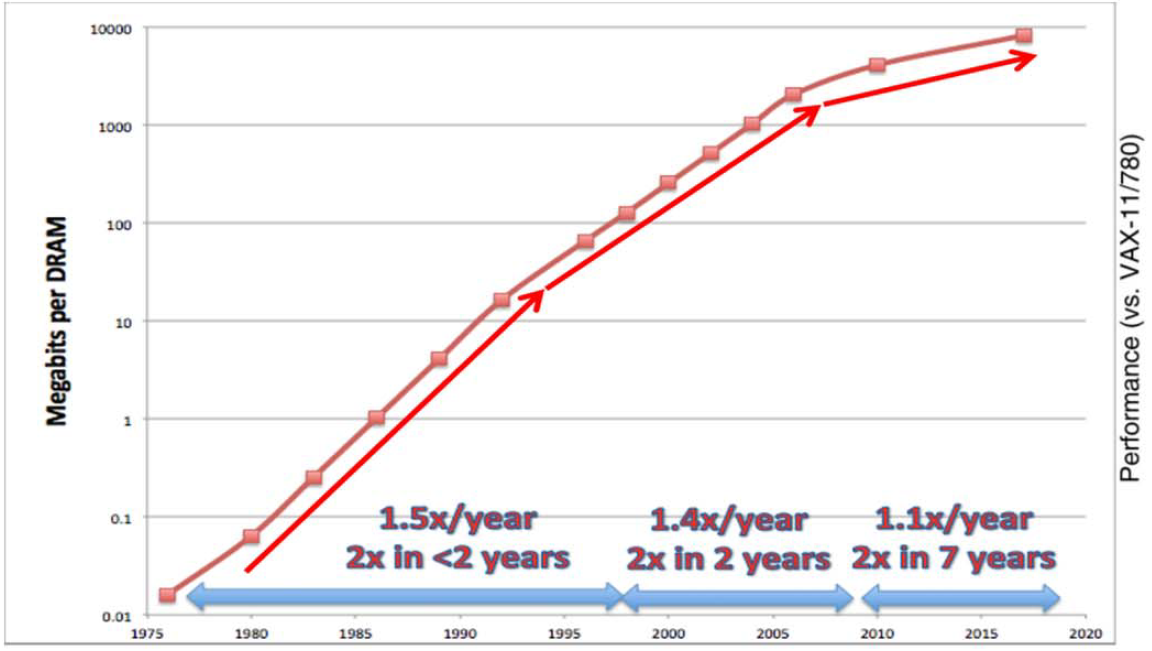

雖然晶片設計和製程技術的創新仍然繼續,但進展已明顯趨緩,不管製程技術下殺到多少微米,晶片尺寸的縮減似乎已到了極限,更遑論同時要增加密度以提升性能。 圖1及圖2是Alphabet的總裁John Hennessy 於2018 年 7 月ERI會議中展示的兩張圖表。圖1顯示了40年間的DRAM的容量和密度增長放緩的情況;而圖2則顯示了40年間的CPU運算性能變化,明顯看出在近年成長已趨於平穩。

半導體產業協會(SIA) 於2016年7月正式宣告ITRS國際半導體技術藍圖時代的結束。其後SIA 和 SRC (半導體研究公司,Semiconductor Research Corporation)於2017 年 3 月聯合發表了名為《半導體研究機會:產業願景和指南》報告(Semiconductor Research Opportunities:An Industry Vision and Guide)。報告中指出:「前進的道路並不像摩爾定律時代那樣清晰,然而,巨大的經濟和社會效益潛力 — 其中一些是可以預見的,但有一些只能想像 …… 在這個關鍵點上,需要產業界、政府和學術界攜手合作,才能持續進步成長。」

應用及市場需求帶動

在今天,電子產品已深深融入我們的社會結構,改變著我們的生活、工作和娛樂方式,讓我們生活在數位時代,為我們的全球生活方式、產業和商業行為帶來高新的效率。而這種效率的達成主要歸功於高效能運算晶片的產出。另一方面,大數據的形成則推動了市場需求,從而形成了技術研發的驅動力。

在現實層面,推動數據增長的市場力量包括:

- 將數據、邏輯和應用程序轉移到雲端

- 社交媒體的推波助瀾

- 行動設備的演變

- 5G/6G 通信加上物聯網 (IoT)帶動

- 人工智慧(AI)、虛擬現實 (VR)及增強現實(AR)的應用

- 自動駕駛汽車的興起及日漸普及

異質整合興起

雖然製程技術的演進已漸漸無法滿足晶片「體積縮小性能提升」的無止境需求,但需求並沒有消失,因此,人們開始往構裝技術動腦筋。

異質整合是指將單獨製造的「組件」整合到更高層次的組裝(系統級封裝 – System in a Package,SiP),以使整體性能提升。系統級封裝不是隨便將兩個晶片封裝在一起就可以,而是必須滿足下列條件才行:

- 封裝後體積必須變小:將不同功能的晶片與被動元件封裝成一顆IC,所以封裝後體積必定比個別數顆IC還小。

- 必須整合不同類型的封裝技術:必須將數種不同類型的封裝技術整合在一起,與單純將多個晶片封裝在一起的小型封裝技術不同。

- 必須包含各種類型的主動與被動元件:必須包含處理器、記憶體、邏輯元件、類比元件等數個晶片,甚至必須將被動元件、連接器、天線等一起封裝進去。[1]

在異質整合的定義中,「組件」指的是任何單元,無論是單顆晶片、MEMS器件、被動元件和組裝的封裝或子系統,都整合在一個封裝中。當中可以涉及到材料、元件類型、電路類型、節點、互連方法等等。

異質整合前景及應用

異質整合可以說是半導體未來的關鍵技術方向,雖然現在許多大廠 (如AMD、Intel、Samsung、華為)的處理器已應用了異質整合的系統級封裝技術,但還是有許多領域有待摸索及發展。

IEEE提出的異質整合藍圖 (HIR) [2]旨在成為系統應用驅動的藍圖,融合整個電子生態系統的市場拉動和技術推動的雙重性;IEEE的HIR確定了異質整合的領先技術驅動力的6個市場應用領域藍圖,分別是:

- 高性能運算和數據中心

- 醫療、健康和穿戴式設備

- 自動駕駛汽車

- 行動電話

- 航空航天和國防

- 物聯網

HIR試圖回答的關鍵問題包括:電子系統中的構建塊(building blocks)是什麼?這些基本的構建塊需要什麼樣的整合技術來維持系統整合正常?HIR設想的構建塊包括:

- 單晶片和多晶片整合(包括基板)

- 集成光子學

- 集成電力電子

- MEMS 和傳感器整合

- 5G 以及模擬和混合信號

這些構建塊的基礎是跨市場應用及技術領域的,含蓋:

- 材料和新興研究材料

- 新興研究設備

- 測試

- 供應鏈

- 安全

- 熱管理

- 共同設計

- 模擬

最後,HIR確定了異質整合的三個主要技術領域,分別是:

- 系統級封裝

- 3D 和 2D 互連

- 晶圓級封裝 – WLP(包括扇入和扇出)

參考資料:

|